Intel Pentium 4 6xx and 3.73EE: Favoring Features Over Performance

by Anand Lal Shimpi & Derek Wilson on February 21, 2005 6:15 AM EST- Posted in

- CPUs

An Interesting Observation: Prescott 2M's Die

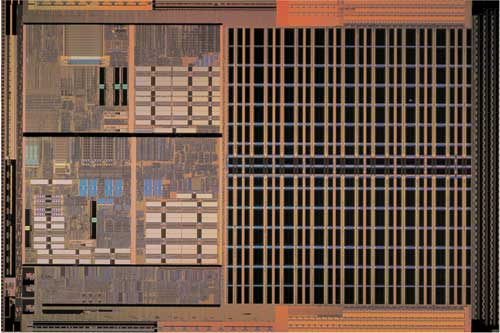

What has been true for a number of modern day microprocessors is that the vast majority of the CPU is made up of cache, take a look at the Athlon 64 FX with its 1MB L2 cache:

AMD Athlon 64 FX die (the large block to the right is its 1MB L2 cache)

Over half of the die is L2 cache.

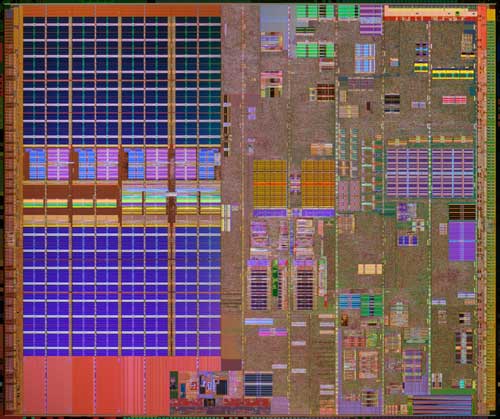

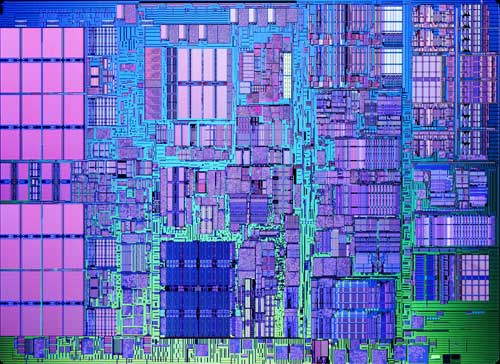

But when looking at the new Prescott 2M core the same can't be said:

Intel Pentium 4 600 series die (the large block to the left is its 2MB L2 cache)

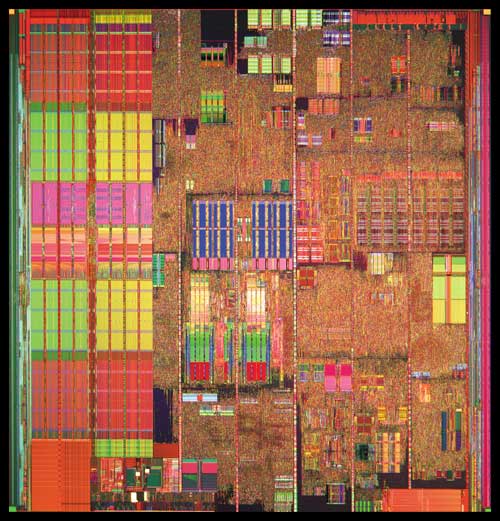

The split between logic and cache is almost 50/50, looking back at the original Prescott we see that the Prescott core itself actually occupied more die area than the cache:

Intel Pentium 4 500 series (the block to the left is its 1MB L2 cache)

There are two explanations for the phenomenon, first with Prescott Intel introduced their highest density cache ever produced; at present day it holds the record for largest cache with the smallest area on a modern desktop microprocessor. Secondly, is the fact that Prescott, with its 31 pipeline stages, 64-bit execution units and highly accurate branch predictors with massive branch history tables, is simply a big, complex core. Also remember that the Athlon 64 is basically a reworked K7 core, with wider execution units and datapaths, as well as an on-die memory controller, so it is understandably simpler.

Let's compare that to the Pentium M:

Intel Pentium M 90nm (the large block is its 2MB L2 cache)

The PowerPC 970 (used in Apple's G5 systems) looks a bit more Prescott like, but remember we're only dealing with a 512KB L2 cache here:

IBM PowerPC 970 (the block to the left is its 512KB L2 cache)

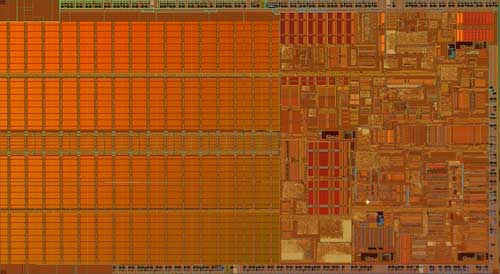

Or, even more interestingly, compare it to the newly announced Cell processor:

IBM/Sony/Toshiba Cell microprocessor (we apologize for the quality of the die shot, it's the best we could find)

Looking at Cell is quite interesting because it appears to be just as complex as Prescott, but remember that with Cell we're looking at 9 individual processors. But more on that next week...

Extreme Edition - Not so "Extreme" Anymore

Back when the Extreme Edition was first launched, the Pentium 4 had a "meager" 512KB L2 cache compared to the EE's 2MB L3 and 512KB L2. Now that the Pentium 4 has a 2MB L2 cache and is based off of the same core as the EE, the only benefit that the Extreme Edition offers is 1066MHz FSB support and a slightly higher clock speed.

We looked at the impact of the 1066MHz FSB in the past and quickly found that it didn't do much for the EE. Although we're now running at 3.73GHz for the Pentium 4 Extreme Edition, the benefit from the 1066MHz FSB is still pretty limited.

As for the clock speed advantage, the fastest Pentium 4 6xx is the 660, running at 3.60GHz - 96.4% of the clock speed of the 3.73GHz Extreme Edition - the clock speed difference is effectively nothing.

But the price? The 3.73 EE will retail for $999, the Pentium 4 660: $605. The Extreme Edition was never a good value, but in the case of the new chip, it's basically throwing money away. Let the benchmarks speak for themselves, but your best bet is to wait for the next generation of Extreme Edition CPUs, either with a 4MB L2 cache or the dual core offerings.

71 Comments

View All Comments

DerekWilson - Monday, February 21, 2005 - link

you are correct mike (and you too mjz5):-)

DerekWilson - Monday, February 21, 2005 - link

You're in luck -- Anand is writing that one personally. In my opinion he's the best there is at explaining technology so that anyone can understand it.And we've got "better" pics of cell, but they have boxes and text all over them to tell what block does what ... that's the best "clean" cell pic we've got.

mjz5 - Monday, February 21, 2005 - link

new news!! Nothing new from intel, actually that's not new news :-s...nourdmrolNMT1 - Monday, February 21, 2005 - link

also, in the Cell picture, i count 8 cache areas, is there 8 sub processors with their own cache and then a main processor that controlls all the others with its own cache (the dark blue on the right, while the light blue is the sub processors cache?)MIKE

nourdmrolNMT1 - Monday, February 21, 2005 - link

:-)yea, find a better quality pic of the Cell processor. and please use small words that the small ppl like me can understand especially in the Cell article next week. i look forward to it, but dont want to be all confused like i am on a lot of your high tech articles.

:-D

MIKE

DerekWilson - Monday, February 21, 2005 - link

I can only fix 89 broken things at a time :-)anything else need tweaking?

nourdmrolNMT1 - Monday, February 21, 2005 - link

nvm post 3, read this post insteadpage 4 = bottom of page 3... fix it.

I ORDER YOU NOW

MIKE

JustAnAverageGuy - Monday, February 21, 2005 - link

It's fun to watch them add the pages one by one :)nourdmrolNMT1 - Monday, February 21, 2005 - link

wrong graphs on page 4???MIKE

AtaStrumf - Monday, February 21, 2005 - link

He, he, no first post for all you first posters >;-)