Platform Strategy: 4x4, Torrenza, Trinity, and Raiden

It wouldn't be fair to completely ignore AMD Live!, as there was a fair amount of time spent talking about it. Unfortunately, AMD Live! is much like Intel's VIIV. That is to say, the "technology" is more of a suggestion about what components to include in computers built for a specific purpose in order to assist in the marketing of an idea. Certainly, the "computer as media center" idea isn't something new. Intel and AMD simply enabled the magic co-branding fairy to make end users feel all warm and squishy inside about their purchase. To be fair, mindshare is a large part of the game, and Centrino has served Intel very well on the mobile front (though I wish this early Centrino I've got had been a Pentium-M with onboard 802.11g).

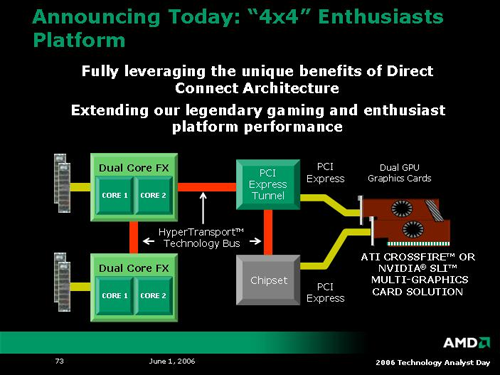

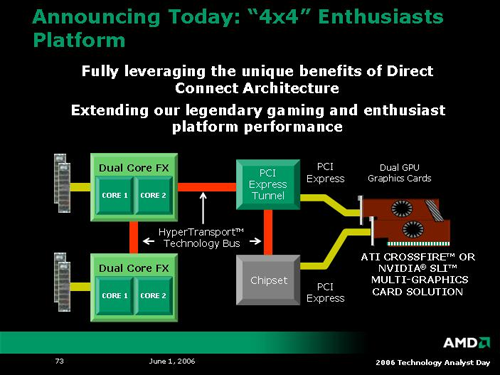

Moving on, there were some very high powered (as in power draw) announcements. First off, AMD is pushing a new high end enthusiast platform consisting of dual socket motherboards for dual core processors combined with quad GPU solutions. In an incredibly unoriginal moment of indiscretion, this platform has been dubbed 4x4. Uninspired, yet very appropriate: the platform will very likely be large, loud, and so power hungry we will need a gas powered generator to run it. That doesn't mean we wouldn't want to own a system. We just aren't sure we'd want to pay for it.

So, the first question we asked about 4x4 was: how much different is this than taking an off the shelf 2P board and dropping in a couple 2xx series Opteron processors with NVIDIA's quad SLI? Unfortunately, we haven't gotten any answer other than to say that there is something that makes it different. From what we understand, 4x4 will support unbuffered DIMMS (while Opterons still require registered memory), and the platform will be focused towards tweakable motherboards. We are looking into all the details. While the more power! kick is always interesting, we have to wonder if there will be any software in the near term that can really harness all this raw potential.

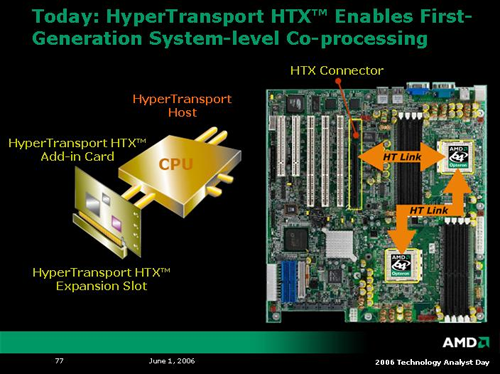

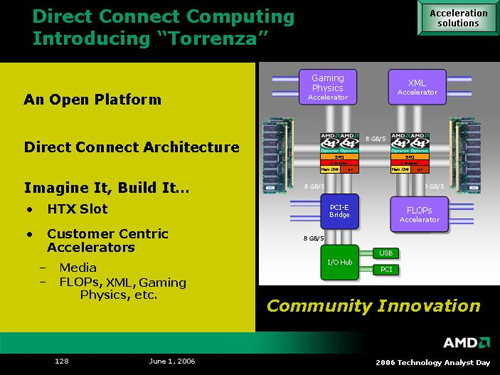

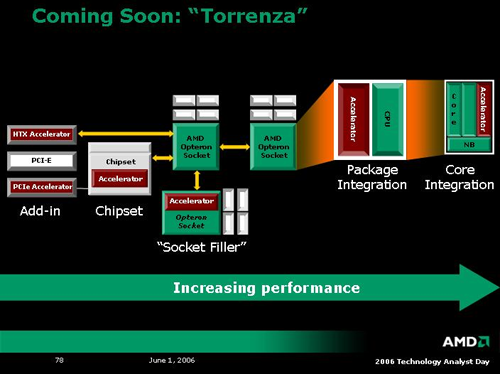

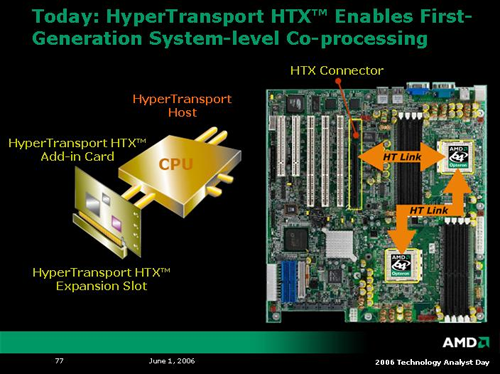

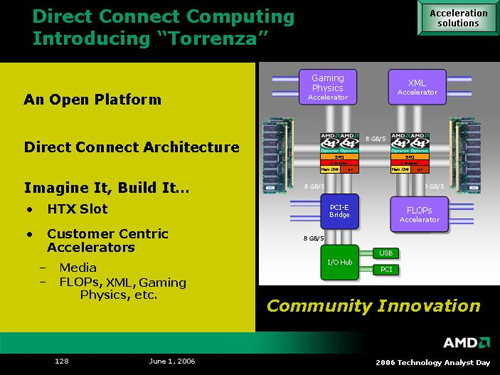

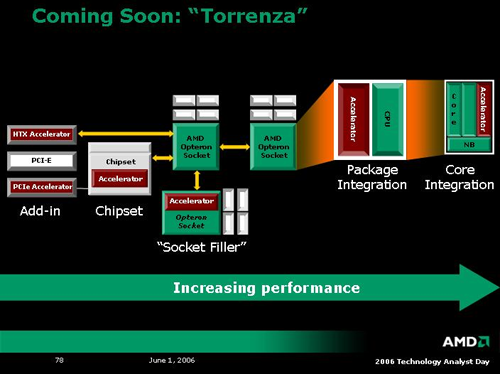

Stepping past the enthusiast platform, we have arguably the most exciting announcement of the day: Torrenza. Along with K8L, AMD plans on openly licensing it's (until now proprietary) coherent HyperTransport technology. At first glance, this may not seem exciting, but AMD is throwing in a little twist: HTX slots. These HTX slots will be standard interfaces connected directly to an AMD CPU's HyperTransport link. If both of these links are coherent, the device and the CPU will be able to communicate directly with each other with cache coherency. Because of this, latency can be reduced greatly over other buses as well, enabling hardware vendors to begin to create true coprocessor technology once again.

In addition to the flexibility of allowing the addition of such "accelerators" (as AMD calls them) to be added in via HTX slots, the architecture of the K8L line will be flexible enough that AMD could choose to incorporate some of these coprocessor technologies on a CPU package, or even on a CPU die itself. This is possible because the interconnect interface is the same at any level of integration. Not only will companies be able to develop their own unique solutions to extend the capabilities of the system processor, but it may even be possible to see such technology integrated into future AMD parts at a more fundamental level.

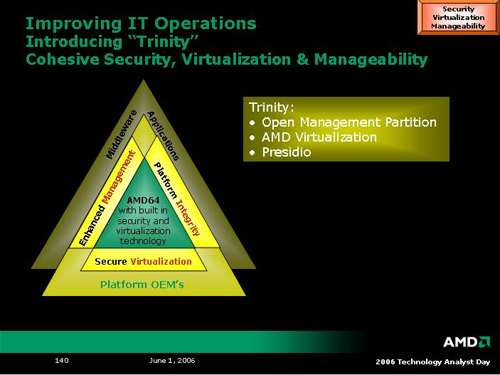

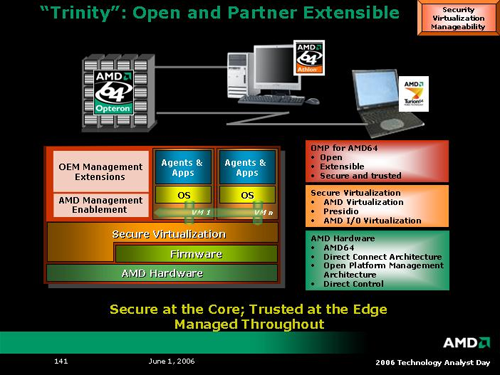

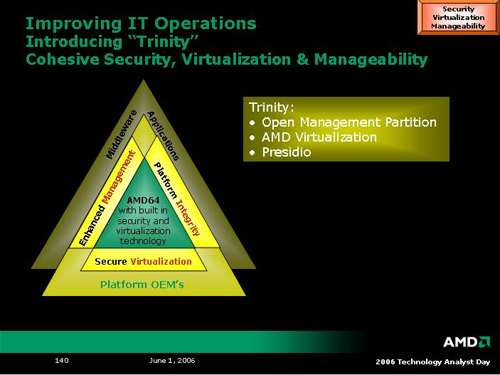

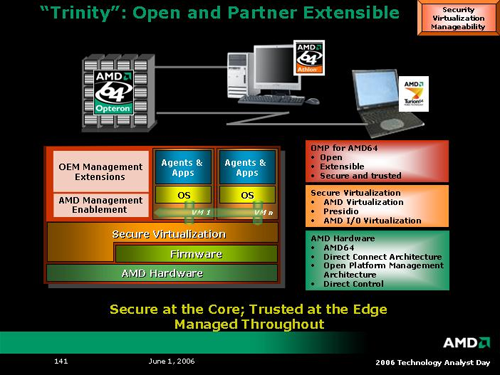

The next two platform level technologies AMD spoke on are named Trinity and Raiden. At many levels, Raiden seems more like an AMD Live! style initiative enabled by Trinity and other technologies, but we're getting ahead of ourselves. At its core, Trinity is AMD's platform level support for hardware virtualization. In addition to previously introduced Pacifica technology, AMD is working with the PCISIG to develop advanced I/O virtualization in addition to enhancing security and manageability of virtualized hardware at every level. The actual hardware that will enable Trinity wasn't explicitly expounded upon, but we did get these two slides with a brief description of how security, manageability and virtualization can't be handled as three separate problems.

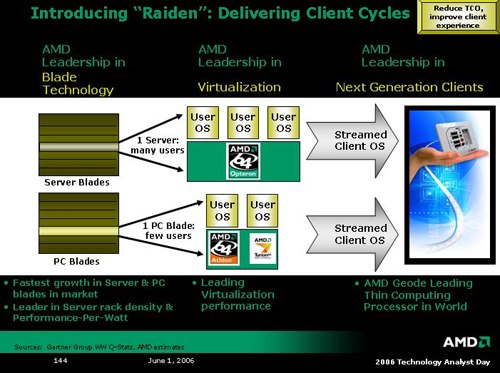

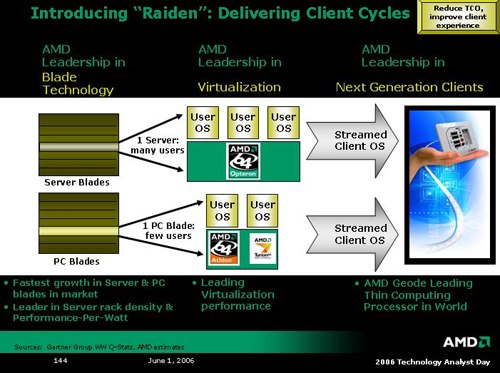

Moving on to Raiden, AMD wishes to change the way businesses look at the way they provide computing to their employees. Rather than hardware, AMD believes businesses would be better served by focusing on compute cycles. Server and PC hardware can be setup in blade-like configurations, and employees can run thin clients which stream their OS from the compute server. Ideally, the reality of where their "compute power" comes from won't be important to the end user as long as there was no difference in experience. Having a large number of under utilized computers is a cost companies could avoid by sharing the processing power of fewer machines over a large number of people.

If there is any technology that is Raiden specific, AMD was not forthcoming. From what we can tell, AMD will leverage the current enthusiasm over blade systems and its Trinity virtualization platform to push customers toward a centralized computational model on the basis of power and cost savings. Certainly the benefits are there if the technology can support it, and hopefully we will be able to get some clarification on how Raiden translates to actual hardware.

It wouldn't be fair to completely ignore AMD Live!, as there was a fair amount of time spent talking about it. Unfortunately, AMD Live! is much like Intel's VIIV. That is to say, the "technology" is more of a suggestion about what components to include in computers built for a specific purpose in order to assist in the marketing of an idea. Certainly, the "computer as media center" idea isn't something new. Intel and AMD simply enabled the magic co-branding fairy to make end users feel all warm and squishy inside about their purchase. To be fair, mindshare is a large part of the game, and Centrino has served Intel very well on the mobile front (though I wish this early Centrino I've got had been a Pentium-M with onboard 802.11g).

Moving on, there were some very high powered (as in power draw) announcements. First off, AMD is pushing a new high end enthusiast platform consisting of dual socket motherboards for dual core processors combined with quad GPU solutions. In an incredibly unoriginal moment of indiscretion, this platform has been dubbed 4x4. Uninspired, yet very appropriate: the platform will very likely be large, loud, and so power hungry we will need a gas powered generator to run it. That doesn't mean we wouldn't want to own a system. We just aren't sure we'd want to pay for it.

So, the first question we asked about 4x4 was: how much different is this than taking an off the shelf 2P board and dropping in a couple 2xx series Opteron processors with NVIDIA's quad SLI? Unfortunately, we haven't gotten any answer other than to say that there is something that makes it different. From what we understand, 4x4 will support unbuffered DIMMS (while Opterons still require registered memory), and the platform will be focused towards tweakable motherboards. We are looking into all the details. While the more power! kick is always interesting, we have to wonder if there will be any software in the near term that can really harness all this raw potential.

Stepping past the enthusiast platform, we have arguably the most exciting announcement of the day: Torrenza. Along with K8L, AMD plans on openly licensing it's (until now proprietary) coherent HyperTransport technology. At first glance, this may not seem exciting, but AMD is throwing in a little twist: HTX slots. These HTX slots will be standard interfaces connected directly to an AMD CPU's HyperTransport link. If both of these links are coherent, the device and the CPU will be able to communicate directly with each other with cache coherency. Because of this, latency can be reduced greatly over other buses as well, enabling hardware vendors to begin to create true coprocessor technology once again.

In addition to the flexibility of allowing the addition of such "accelerators" (as AMD calls them) to be added in via HTX slots, the architecture of the K8L line will be flexible enough that AMD could choose to incorporate some of these coprocessor technologies on a CPU package, or even on a CPU die itself. This is possible because the interconnect interface is the same at any level of integration. Not only will companies be able to develop their own unique solutions to extend the capabilities of the system processor, but it may even be possible to see such technology integrated into future AMD parts at a more fundamental level.

The next two platform level technologies AMD spoke on are named Trinity and Raiden. At many levels, Raiden seems more like an AMD Live! style initiative enabled by Trinity and other technologies, but we're getting ahead of ourselves. At its core, Trinity is AMD's platform level support for hardware virtualization. In addition to previously introduced Pacifica technology, AMD is working with the PCISIG to develop advanced I/O virtualization in addition to enhancing security and manageability of virtualized hardware at every level. The actual hardware that will enable Trinity wasn't explicitly expounded upon, but we did get these two slides with a brief description of how security, manageability and virtualization can't be handled as three separate problems.

Moving on to Raiden, AMD wishes to change the way businesses look at the way they provide computing to their employees. Rather than hardware, AMD believes businesses would be better served by focusing on compute cycles. Server and PC hardware can be setup in blade-like configurations, and employees can run thin clients which stream their OS from the compute server. Ideally, the reality of where their "compute power" comes from won't be important to the end user as long as there was no difference in experience. Having a large number of under utilized computers is a cost companies could avoid by sharing the processing power of fewer machines over a large number of people.

If there is any technology that is Raiden specific, AMD was not forthcoming. From what we can tell, AMD will leverage the current enthusiasm over blade systems and its Trinity virtualization platform to push customers toward a centralized computational model on the basis of power and cost savings. Certainly the benefits are there if the technology can support it, and hopefully we will be able to get some clarification on how Raiden translates to actual hardware.

40 Comments

View All Comments

HurleyBird - Friday, June 2, 2006 - link

HyperTransport was created by AMD. The consortium was created afterwards to manage the standard.

od4hs - Friday, June 2, 2006 - link

AMD began developing the HyperTransport™ I/O link architecture in 1997.Pre-Consortium Versions of the Specification

AMD has released these two pre-consortium documents which define two revisions of "LDT" (Lightning Data Transfer) as HT was known before the HT Consortium was formed.

http://www.hypertransport.org/tech/tech_specs.cfm">http://www.hypertransport.org/tech/tech_specs.cfm

[2001]

AMD has disclosed HyperTransport technology specifications under non-disclosure

agreement (NDA) to over 170 companies interested in building products that incorporate

this technology.

Multiple partners have signed the license agreement for HyperTransport technology,

including, among many others:

Sun Microsystems Cisco Systems Broadcom

Texas Instruments NVIDIA Acer Labs

Hewlett-Packard Schlumberger Stargen

PLX Technology Mellanox FuturePlus

API Networks Altera LSI Logic

PMC-Sierra Pericom Transmeta

AMD is releasing the specifications to an industry-supported non-profit trade association in the fall of 2001.

The HyperTransport Consortium will manage and refine the specifications, and

promote the adoption and deployment of HyperTransport technology. It is also expected

to consist initially of a Technical Working Group and a Marketing Working Group.

Subordinate task forces will do the work of the consortium. Anticipated technical task

forces include:

Protocol Task Force

Connectivity Task Force

Graphics Task Force

Technology Task Force

Power Management Task Force

Information on joining the HyperTransport Technology Consortium can be found at

this website: http://www.hypertransport.org">http://www.hypertransport.org

http://www.amd.com/us-en/assets/content_type/white...">HyperTransport Technology I/O Link (white paper), PDF

San Jose, Calif., July 24, 2001 -- A coalition of high-tech industry leaders today announced the formation of the HyperTransport™ Technology Consortium, a nonprofit corporation that supports the future development and adoption of AMD's HyperTransport I/O Link specification.

[...] More than 180 companies throughout the computer and communications industries have been engaged with AMD in working with the HyperTransport technology

http://www.hypertransport.org/consortium/cons_pres...">hypertransport.org press release

peternelson - Friday, June 2, 2006 - link

HT 1,2,and 3 are published standards.

Direct Connect Architecture (DCA 1.0 and 2.0 are published standards).

HTX is a published standard.

Some questions for you to ask the AMD engineers:

I'm still interested to obtain pinouts of AM2 and F1207 sockets to establish how many HT links they can support.

From 4x4 it looks like AM2 *MIGHT* support TWO HT links (one to other processor, one to the tunnel chip.

I note 4x4 is slated for 2006 launch.

Hope to see those boards real soon ;-) I assume you can populate one socket and put the other proc in there later when you have more money ;-)

I would like to see HTX appear on some 4x4 or AM2 boards but doubt it will happen.

However, on the "acceleration technology" I would like 4x4 to support the so-called "socketfiller" type where you drop in a xilinx fpga onto the socket. That would give a cheap 1cpu + 1fpga system. Hopefully acceleration is not precluded just cos its not opteron and not 1207.

Now thinking of opterons, I want to know the pinout of socket F. I want to count the HT link support built in to the socket. If its only 3 HT links that would force a socket change to do 4 links.

What news on possible future socket change requirements? eg for ddr3 and HT3 speed?

Can the Nvidia chipset for opteron be built onto an AM2 board?

I would encourage many board makers to add HTX to their opteron boards (easy and worthwhile) because eg one example is the pathscale HTX cluster interconnect cards.

I am interested in AMD terms for licensing of any proprietary tech for their cache coherency, or DCA2, any white papers on it or reference designs.

Is the 4x4+ in 2007 only K8 quadcore or is it K8L quadcore?

Will K8L be supported on AM2 socket?

Please encourage AMD to publish web datasheets on AM2 as exist for their old sockets.

saratoga - Friday, June 2, 2006 - link

I think any HT compliant chipset can be used with any HT compliant part. Thats why Apple can use AMD's PCI-X bridge designed for Opteron processors on their older G5 systems. The chipset supports HT, thats all you need.

I don't know if that changes with the new HT standards though.

peternelson - Friday, June 2, 2006 - link

*IF* an am2 socket can indeed support TWO HT links, then the SECOND processor could use its spare link to connect to yet another I/O interface chip/chipset.This would give opportunity for innovative 4x4 boards to add additional I/O, more pcie links, or an HTX slot.

Please can we verify:

How many links are available on AM2, and howmany links are available on FX62, and how many links are available on lower AM2 chips. I suspect the lower ones only have one HT link which would make them unsuitable for 4x4 operation. Please confirm.

Jellodyne - Friday, June 2, 2006 - link

There's a few of ways 4x4 could work with only the one HTT link in the socket.1. AMD could enable a second chip-to-chip HTT link using pins/lands on top of the cpu, or some sort of edge connector, with a pcb which bridges the two.

or

2. AMD could be splitting the HTT link into 2 8-bit links. One to the chipset, one to the 2nd processor. Heck, if the chipset is smart enough the leftover 8 bit link could go back to the chipset, resulting in the equivalent bandwidth between chipset and processors as a 'standard' dual opteron rig, just less between the processors. For desktops, 8 bit is probably enough.

and of course if you're talking custom chipset, that leaves

3. The chipset has dual CHT links, one to each processor, and acts like a traditional dual FSB chipset.

I'd say #2 is pretty likely.

Squidward - Friday, June 2, 2006 - link

Whoever designs those slides should be fired or at least taught some color coordination. They hurt my eyes.Now dual slot - dual core mobos sound tasty but the price would be astronimical to configure a killer system. (looks at outdated Athlon 2500+ and sighs)

Calin - Monday, June 5, 2006 - link

(looks at outdated Duron 600 and cries)LoneWolf15 - Monday, June 5, 2006 - link

Time to draw the L1 bridges shut and clock your way up, my friend.My Duron 600 made 1GHz when cooled right --it was cooler at 7.5 x 133 than at 10.0 x 100.

And if you fry the chip, well...a used Duron, Thunderbird, or Palomino core is relatively inexpensive these days...

Frallan - Monday, June 5, 2006 - link

Well at least U guys have saved some money on the way of beeing outdated...*looks at outdated 3500+, 6800Gt@Ultra, 2*1Gb Ram and empty wallet and howls with pain*

/F