The Quest for More Processing Power, Part Three: "Multi core of Intel and AMD compared"

by Johan De Gelas on May 18, 2005 3:15 PM EST- Posted in

- CPUs

Dual core Opteron versus Pentium-D and Dempsey

There is no doubt that the Dual core Opteron architecture is more advanced and elegant than the Pentium-D and even future Netburst based dual cores such as Dempsey (Xeon). The Pentium-D Dual core is more a way of packaging than an actual architecture: two cores cut out the wafer together, and communicate via an external FSB.With two different L1 and L2-caches, and two CPUs working on the same variables, you risk that one of the CPUs is working on an outdated cached value. You need to make sure that if variable A is cached on both CPUs, and CPU 1 changes the value of variable A, then CPU 2 knows about it. This happens with a protocol called MESI on the Intel CPUs and MOESI on the AMD CPUs. The discussion of these “cache coherency protocols” is outside the scope of this article, but you understand that the more variables that are shared between the two CPUs, the more communication that will happen between the caches of the different CPUs.

In the case of the Pentium-D, the caches talk to each other (to keep cache consistency) via a shared 800 MHz bus, just like two single core SMP Xeons. Not only is 800 MHz relatively slow compared to the CPU (3200 MHz), but exchanging information via a bus also increases latency and lowers bandwidth. Latency is increased as the bus may not always be free - one of the CPUs might be using it to transfer data to or from the memory. This half duplex bus can only transmit signals of one device (CPU 1, CPU 2, chipset) at a given moment. Bandwidth is decreased as the cache coherency exchanges need a small amount of time on the bus too.

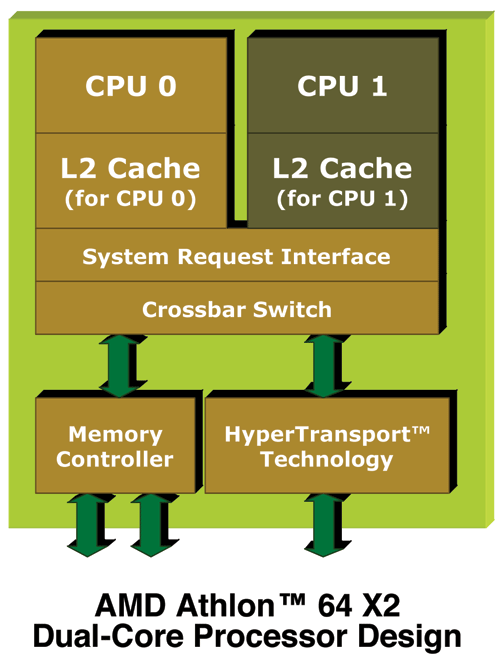

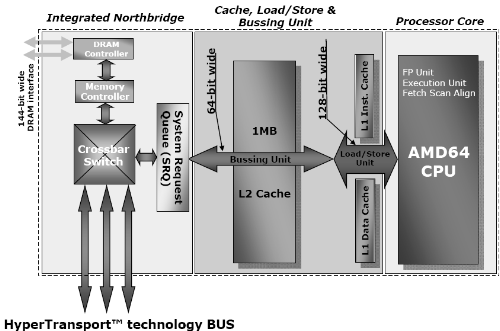

Enter the elegant dual core Opteron architecture. Each core in the Dual Opteron/Athlon 64 X2 puts its request on the System Request Queue (SRQ).

28 Comments

View All Comments

Houdani - Wednesday, May 18, 2005 - link

'Splain to me what you believe are the alleged "false assumptions."The only outright assumption I observed was located in the comments section. Specifically number two.

Ahkorishaan - Wednesday, May 18, 2005 - link

Intel is by no means panicking, they're riding out a storm, and things will be dicey starting about 2/3 through 2006. AMD has the advantage now, but I honestly don't know if they can hold up against the R&D budget Intel has at it's fingertips.When P-m features get integrated into Intel's lineups AMD will be faced with the hotter, hungrier chip, and though they have more experience with the on-die Memory controller, and a nice head of steam, that might not be enough.

I'm a fan of AMD and I applaud their foresight, but they need to keep on the ball if they expect to stay ahead for another year.

allanw - Wednesday, May 18, 2005 - link

All this talk of databases and no mention of PostgreSQL? Cmon..flatblastard - Wednesday, May 18, 2005 - link

Oh great....more fuel for the "Intel panics" thread fire.Rand - Wednesday, May 18, 2005 - link

I haven't finished the article yet, but would you care to clarify your objections Questar?At least through the third page I haven't come across any assumptions or even real solid opinions he's put forth as yet.

Thus far it's merely a technically oriented analysis of their respective offerings, nothing that I've read is particularly new or debateable/controversial.

Rapsven - Wednesday, May 18, 2005 - link

Holy ****, Questar. That's all I'm going to say for you.Very informative. Though a lot of the more technical parts of the article flew right by me.

Questar - Wednesday, May 18, 2005 - link

Wow, another AMD fanboy opinion piece based upon false assumtions. Go Anandtech!sprockkets - Wednesday, May 18, 2005 - link

not this time...nice pic on the last page, but I have no idea of the scale